经典的摩尔定律指出,集成电路上可容纳的晶体管数目大约每隔两年就会增加一倍。尽管近年来“摩尔定律失效”的声音不断,但晶体管的数量依然在快速增长。那么,晶体管越多,芯片的性能就一定越强吗?

晶体管越多,功能越丰富

现代芯片的集成度极高,在一个现代处理器中,可能拥有数亿、数十亿甚至数百亿个晶体管,其已不单纯是CPU,而是一套SoC片上系统。以移动SoC为例,除了常见的CPU和GPU,还包含音频解码器、基带/视频前端、调制解调器、数字信号处理器、片上网络、人工智能、温度传感器、显示引擎等众多模块,而这些模块都是基于晶体管构建的。所以,芯片中的晶体管数量越多,就能容纳更多的功能模块,从而在一块芯片中实现以往需要多块芯片才能完成的工作。

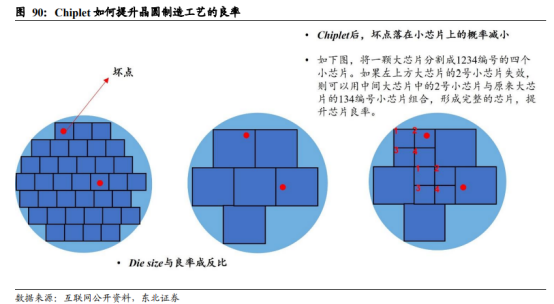

然而,并非无脑增加晶体管就能提升性能。更多的晶体管会产生更多热量,增大功耗,同时芯片尺寸也会变大,这带来了两个严峻的问题。其一,需要更强大的散热系统,并且对周边硬件设计要求更高;其二,降低了生产良率。要知道,芯片是从晶圆上切割下来的,假如一个晶圆上有1个故障块,切割100块芯片的良品率是99%,而切割10块芯片的良品率就降到了90%。在规模效应的放大下,这种成本差异不容忽视。所以,总体上晶体管越多越有利于制造强大的芯片,但成本限制了在特定工艺下晶体管的数量上限。

这便是不断缩小晶体管尺寸的关键原因,更小的晶体管能够更密集地封装在更小的芯片上,进而提升速度、功率,并提高效率。

制造工艺是关键,应用方向要正确

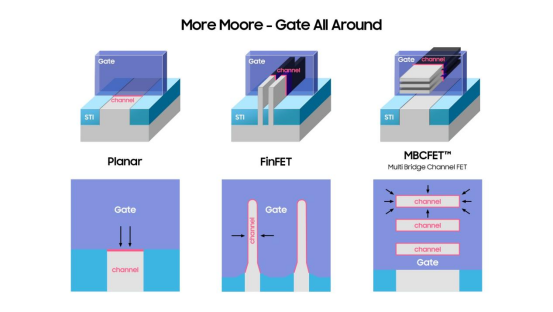

那么,怎样缩小晶体管的尺寸呢?这就要提到大家熟悉的“制程”,比如7nm、5nm等。过去,制程指的是晶体管栅极的最小宽度,随着制程和工艺的进步,特别是FinFET技术的引入,制程数字更多地具有了营销价值,不再确切代表技术意义。不过,我们仍能通过数字大小来判断制程的先进程度,数字越小,晶体管越小,工艺越先进。

制程的提升使得芯片中的晶体管越来越小,从而获得更快的反应速度和更低的控制电压。这意味着我们既能提高芯片的频率来增强性能,也能降低功耗以减少发热和延长续航。

所以在比较两颗芯片时,首先不是看谁的晶体管更多,而是看谁的制程更先进。而且要注意,即使制程相同,晶体管多的也不一定性能更强。比如同为台积电7nm制程的骁龙865和苹果A13,前者晶体管数量达103亿,后者只有85亿,但苹果A13的性能明显更优。

实际上,除了移动芯片,大多数芯片对先进制程的需求并不大,很多芯片用微米级制程制作就能满足需求。但由于产业规模效应,为实现成本效益最大化,只能跟随主流工艺,使得制程不断推进。虽然从技术角度看,很多时候并非必要,但从商业角度,这样做能获取更多收益。所以商用芯片总体上还是朝着晶体管更小更密集的方向发展。

目前,制程的进步已接近物理极限,无论是缩小晶体管沟道带来的热力学极限,还是量子隧穿现象,都会增加晶体管失效的风险。目前的研究表明,1nm是单个硅晶体管的理论极限,如果材料化学没有突破,或许五年后我们就无法再通过增加晶体管来提升性能了。